What is SRAM?

SRAM이란 Static Ramdom Access Memory로 앞의 글자 빼고 저번 포스팅의 DRAM과 같습니다.

DRAM과 똑같이 전원이 공급되어야 기억되는 장치(Volatile)이지만,

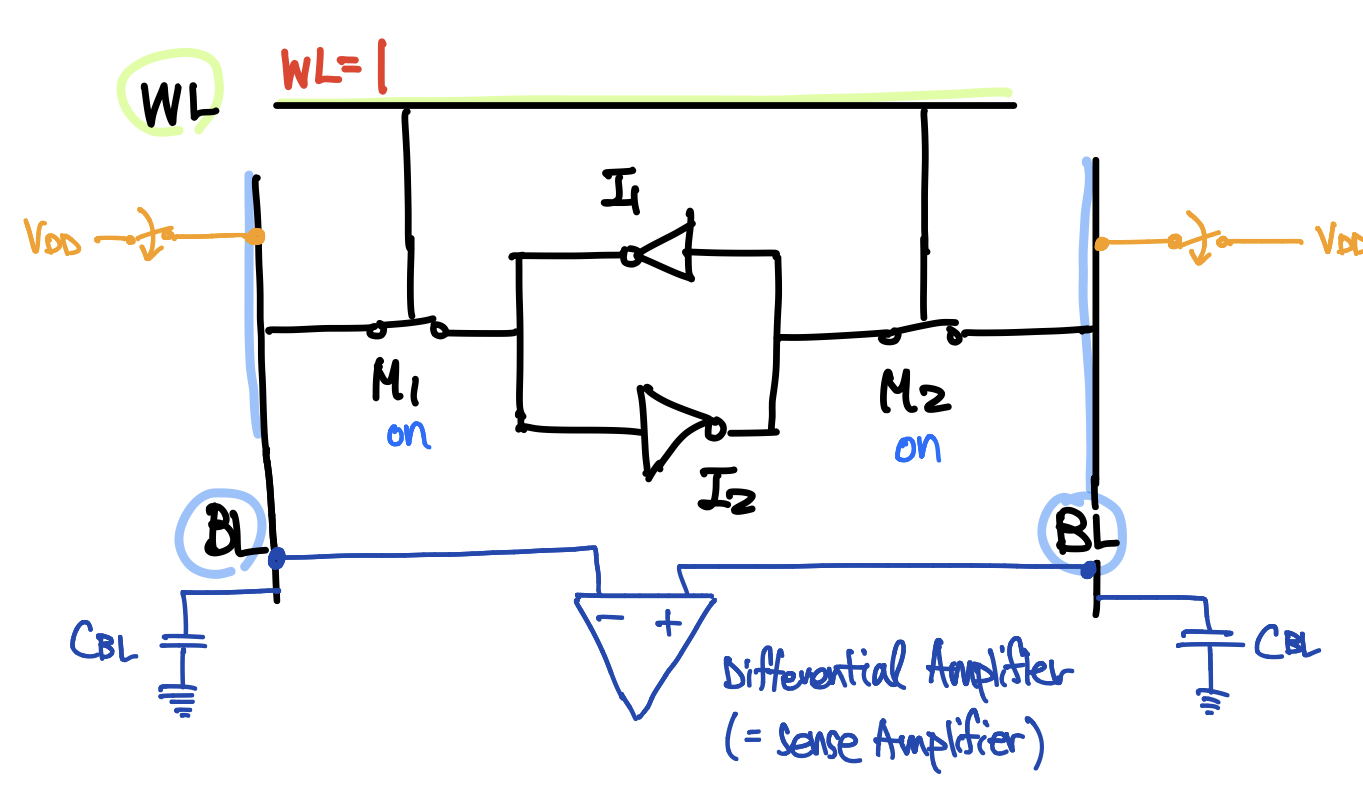

다른 점으로는 Refresh 동작이 필요없습니다. I1, I2 Inverter가 cross-couple 되어있는 곳이 플립플롭 방식으로 메모리를 하기 때문입니다.

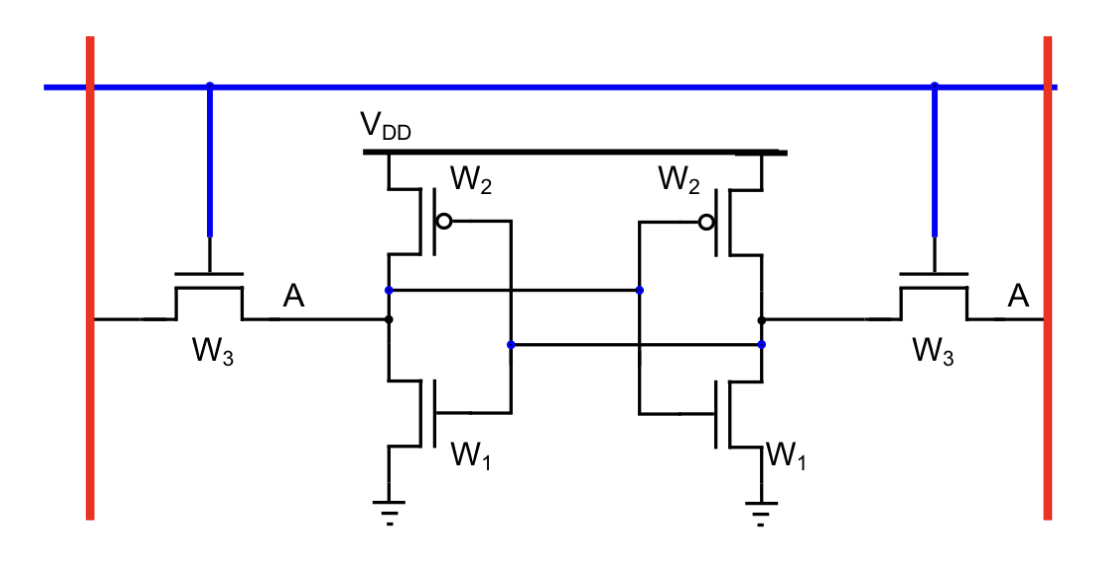

각 인버터는 2개의 transistor을 가지므로(아래 그림) SRAM은 기본적으로 6T SRAM Cell이 되고,

작동에는 3가지 1. hold 2. write 3. read 가 있습니다.

- WL = 0 : hold operation

- WL = 1 : read or write operation

Hold mode

MOS 하나는 switch로 바꿔서 볼 수 있는데 'WL = 0'인 경우에 M1과 M2가 off된 상태로 볼 수 있습니다.

양쪽이 off이므로 coupled-inverter 안에서 계속 값이 도는 것을 확인할 수 있습니다. 이렇게 값이 계속 유지되는 성질에 의해서 Static이라는 단어라 붙은거로 볼 수 있습니다.

Read mode

Hold와 반대로 'WL = 1'이 되어 bit line과 invertor 부분이 연결되는 것을 확인할 수 있습니다.

과정은 다음과 같습니다.

- Precharge BL to Vdd & set WL = 1

- Access internal node with BL/BLB

- Diff. Volt at BL/BLB is amplified by sense amplifier

- Output is either Vdd or Gnd

1, 2번을 보면 간단하게 말해서 switch를 on 시켜서 inverter 안에서 돌고 있던 값을 읽는 것으로 확인할 수 있습니다.

3, 4의 과정의 경우 부가적인 설명이 필요한데,

SRAM Bit cell들은 굉장히 작게 설계가 되어있습니다. 사이즈를 작게 하는 면에서도 이점이 있고, leakage currents를 작게하는 장점을 가지기 위해서입니다. 그런데 이런 작은 사이즈로 인해서 logic '1', '0'을 판단하기 힘들어집니다(매우 작은 신호).

이 문제를 해결하기 위해서 both bit-line들을 Vdd(logic 1)로 precharge를 해줍니다. 각 cell은 BL에 작은 시간동안 작은 diff voltage로 연결이 되는데, Sense Amp로 이런 작은 신호들을 Vdd(logic 1) and Gnd(logic 0)로 바꿔서 다른 MUX나 I/O에 들어가게 해줍니다.

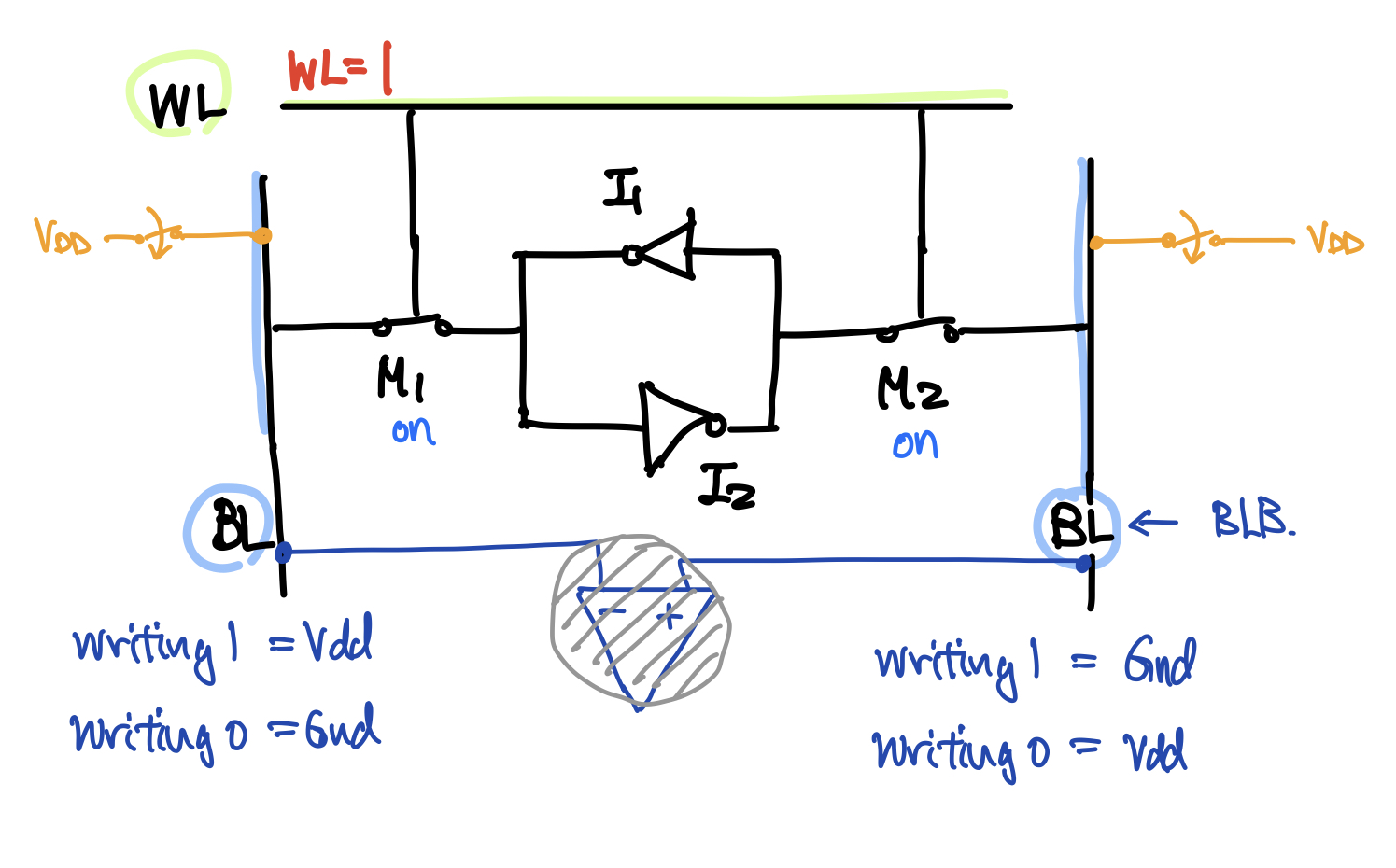

Write mode

Read mode와 동일하게 'WL = 1'인 상태에서 진행되지만 SA(Sense Amp)를 사용하지 않습니다.

그림으로만 봐도 확인할 수 있는데, WL = 1로 set하고 작성할 값을 BL에 주면 Write가 됩니다.

여기까지는 SRAM의 기본적인 동작들과 특성을 알아보았고, 각각 Read/Write에서 주의할 점과 지켜야 할 condition에 대해서 알아보겠습니다.

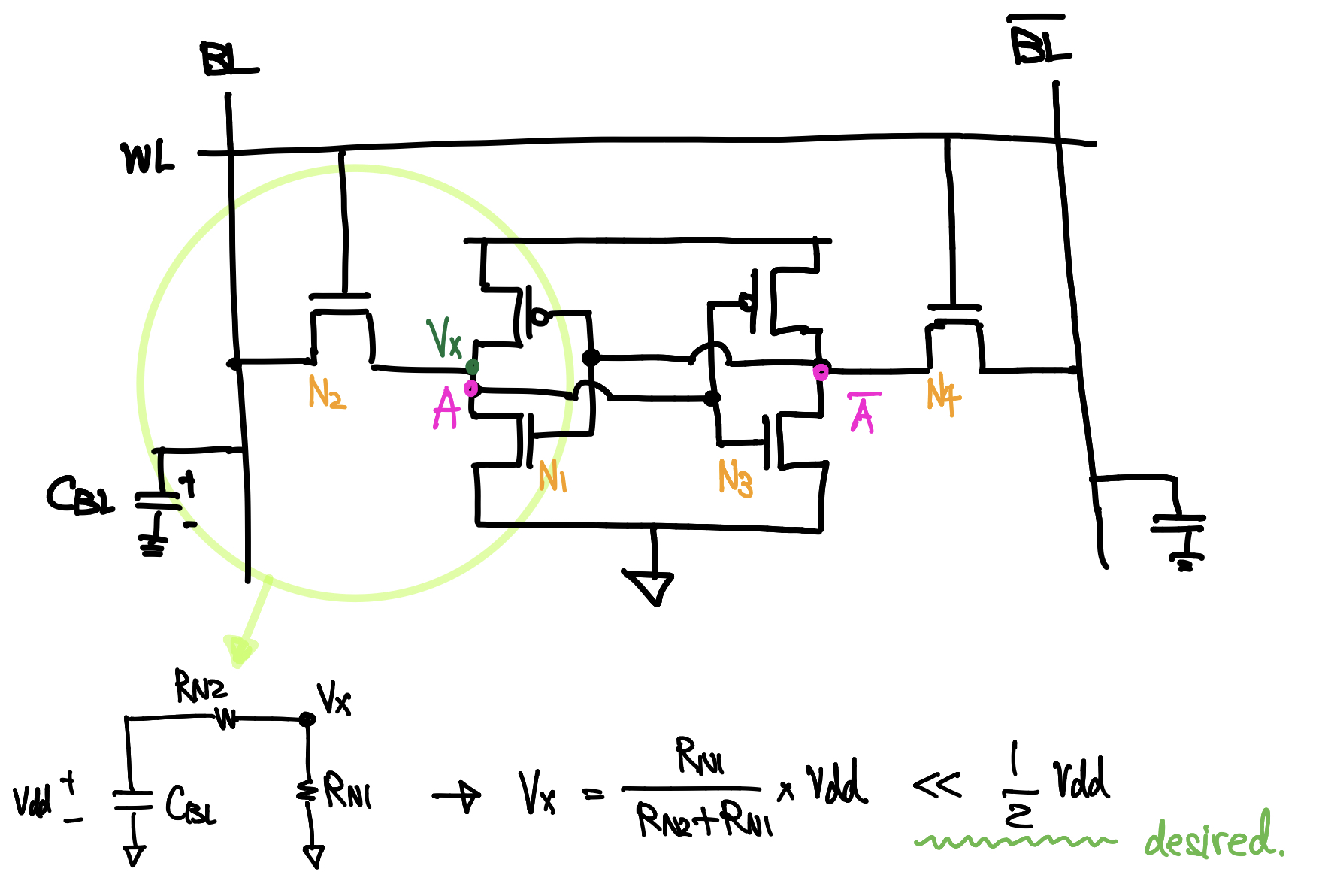

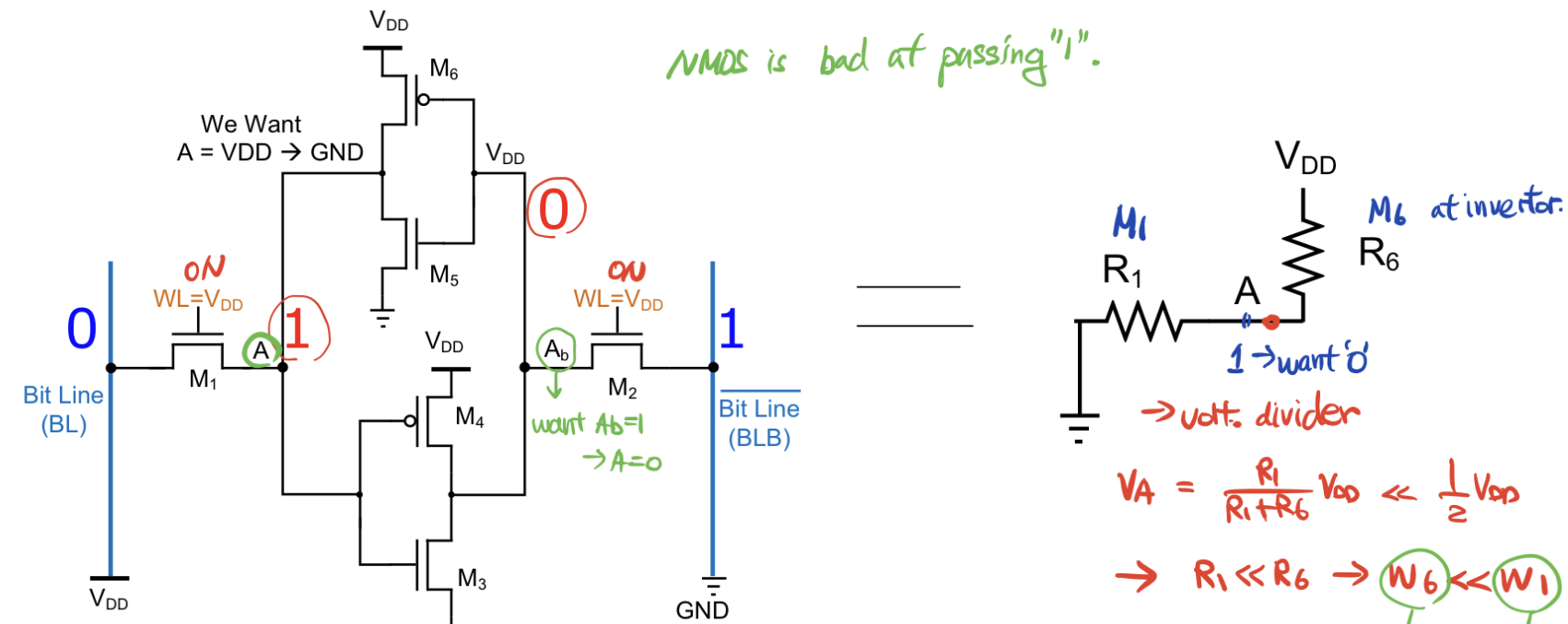

Challenge in Read mode

그림이 복잡해 보이지만 매우 간단합니다.

우선 인버터들을 tr로 풀어서 그렸는데, ON인 상태에서 저항으로 tr을 보게 된다면 각각 N1, N2의 저항으로 볼 수 있습니다. 이 때 Precharge한 Vdd가 voltage divide가 됩니다(그림의 아랫부분).

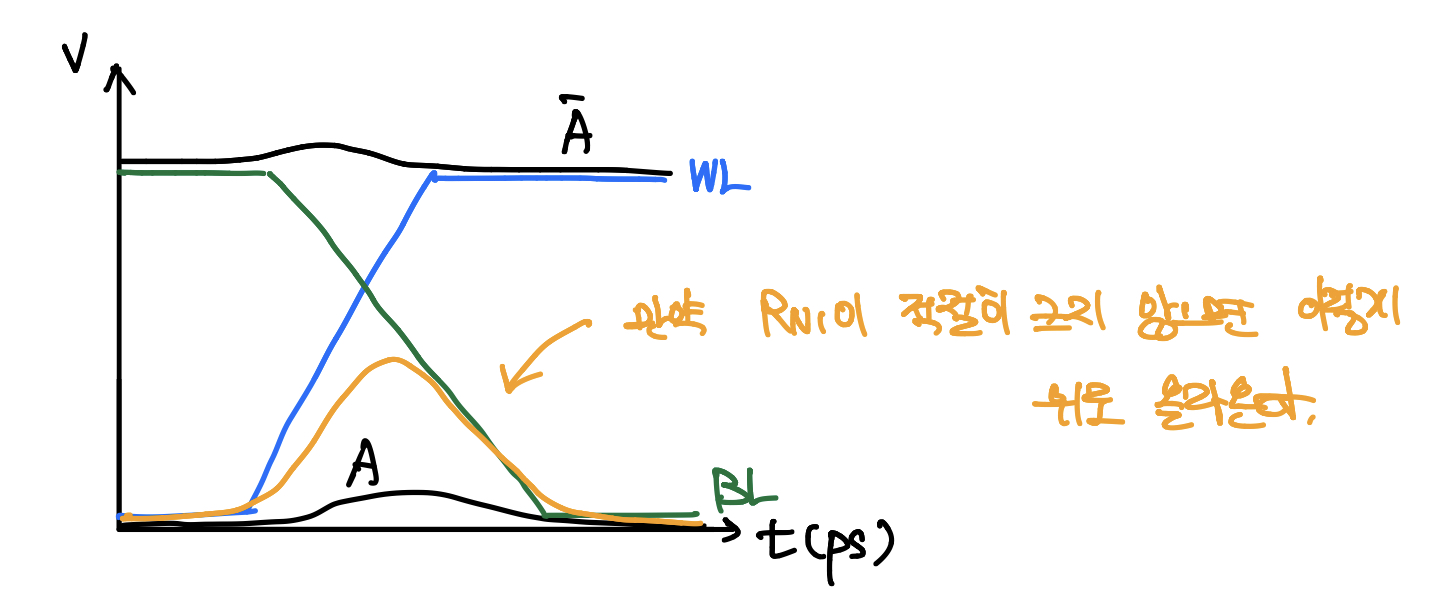

여기서 Vdd*1/2 보다 작은 값이 되기를 원합니다. 그 이유로는 'WL = 1'을 하게되면 (A)(그림) 값에 bump가 생기는데 N1 저항의 값이 크지 않으면 이 값이 크게 튀어 A가 flip되는 현상이 생깁니다. (아래 그림 참고)

위 그림처럼 A, ~A가 그려지는 것이 정상이지만, Rn1이 작다면 Rn2가 작다면 주황색 그래프처럼 A가 bump가 크게 나타날 수 있다.

따라서 N1과 N2의 width를 결정할 때, N1 >> N2가 되게 만들어준다. (mosfet - 저항 참고)

Challenge in Write mode

새로운 값을 줄 때, 내부의 inverter를 overpower해야 합니다. (목적)

Read mode에서와 비슷하게 R1의 저항이 커야하기 때문에 width를 결정할 때, N1 >> N6가 되게 만들어준다.

요약하면

- W1 >> W3 : High BL must not overpower inverters during READ

- W3 >> W2 : Low BL must write new values

위와 같은 관계가 나오는 것을 확인 할 수 있습니다.

출처 :

What is the basic idea behind the SRAM sense amplifier? Why do we need such an exotic circuit solution?

Read 7 answers by scientists to the question asked by Cyril Mechkov on Mar 23, 2018

www.researchgate.net

www.researchgate.net/publication/275061790_SRAM_precharge_system_for_reducing_write_power

(PDF) SRAM precharge system for reducing write power

PDF | This paper presents the static random access memory (SRAM) precharge system by using an equaliser and a sense circuit. Recent goals of designing... | Find, read and cite all the research you need on ResearchGate

www.researchgate.net

allthingsvlsi.wordpress.com/2013/04/19/6t-sram-operation/

6T SRAM Operation

I have the basic Read and Write operation of a 6T SRAM Cell below with figures. Note: i) N1 >> N2 >> P1 ii) There are other explanations with the transistors named M1, M2 etc. I think…

allthingsvlsi.wordpress.com

'Electronic_Engineering > Electric Circuit' 카테고리의 다른 글

| [반도체] ReRAM 알아보기 (RRAM) (3) | 2021.01.08 |

|---|---|

| [반도체] DRAM 알아보기 (0) | 2020.12.28 |

최근댓글