이번 방학 프로젝트로 Vector Machine 설계에서 RRAM Array 파트를 맡았다.

기록을 위해서 블로그에 작성을 할 것인데, 전체적인 내용정도만 보여주고 세부적인 것은 다음에 Virtuoso 튜토리얼 포스팅을 할때 작성해보도록 하겠습니다.

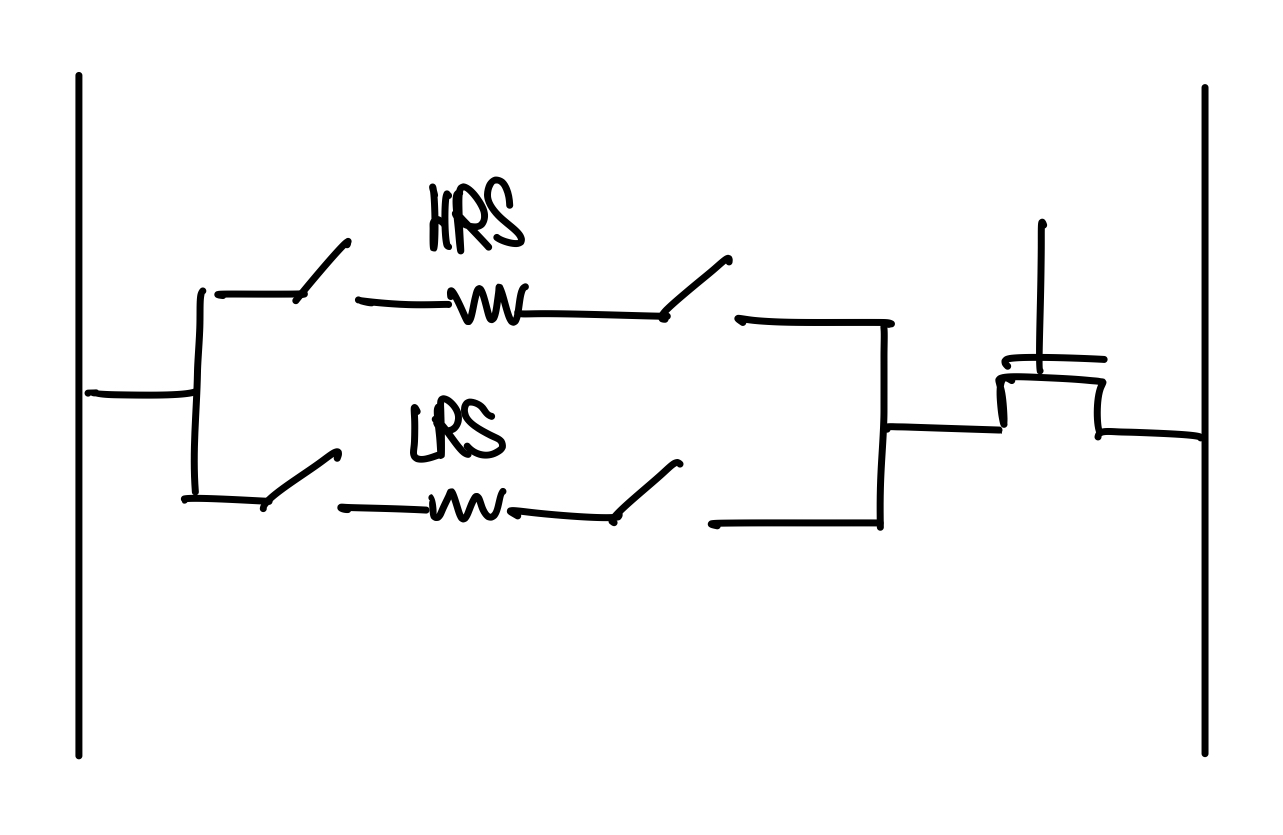

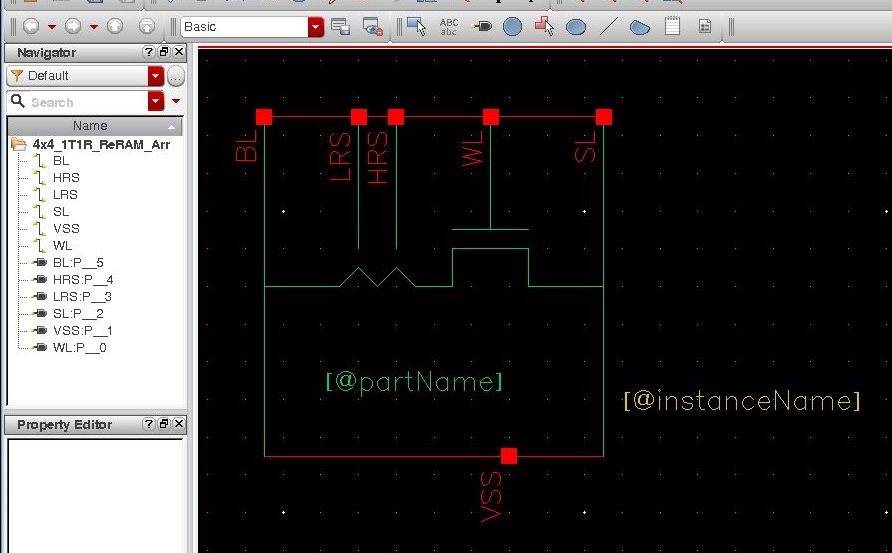

RRAM Array를 만들건데 문제는 RRAM이 아직 상용화되지 않았기 떄문에 PDK에 정보가 없다. 따라서 RRAM과 유사동작하도록 만들어서 설계를 할 것 인데, 아이디어는 저항 두개에 스위치를 이용해서 비슷하게 만들 것 입니다. (아래그림)

실제로는 1T1R이지만 instance가 없기 때문에... :p

각각 HRS와 LRS 저항으로 사용하는 것은 논문을 참고하여 대략 1k 100k 정도로 사용합니다. (RRAM 알아보기 참고)

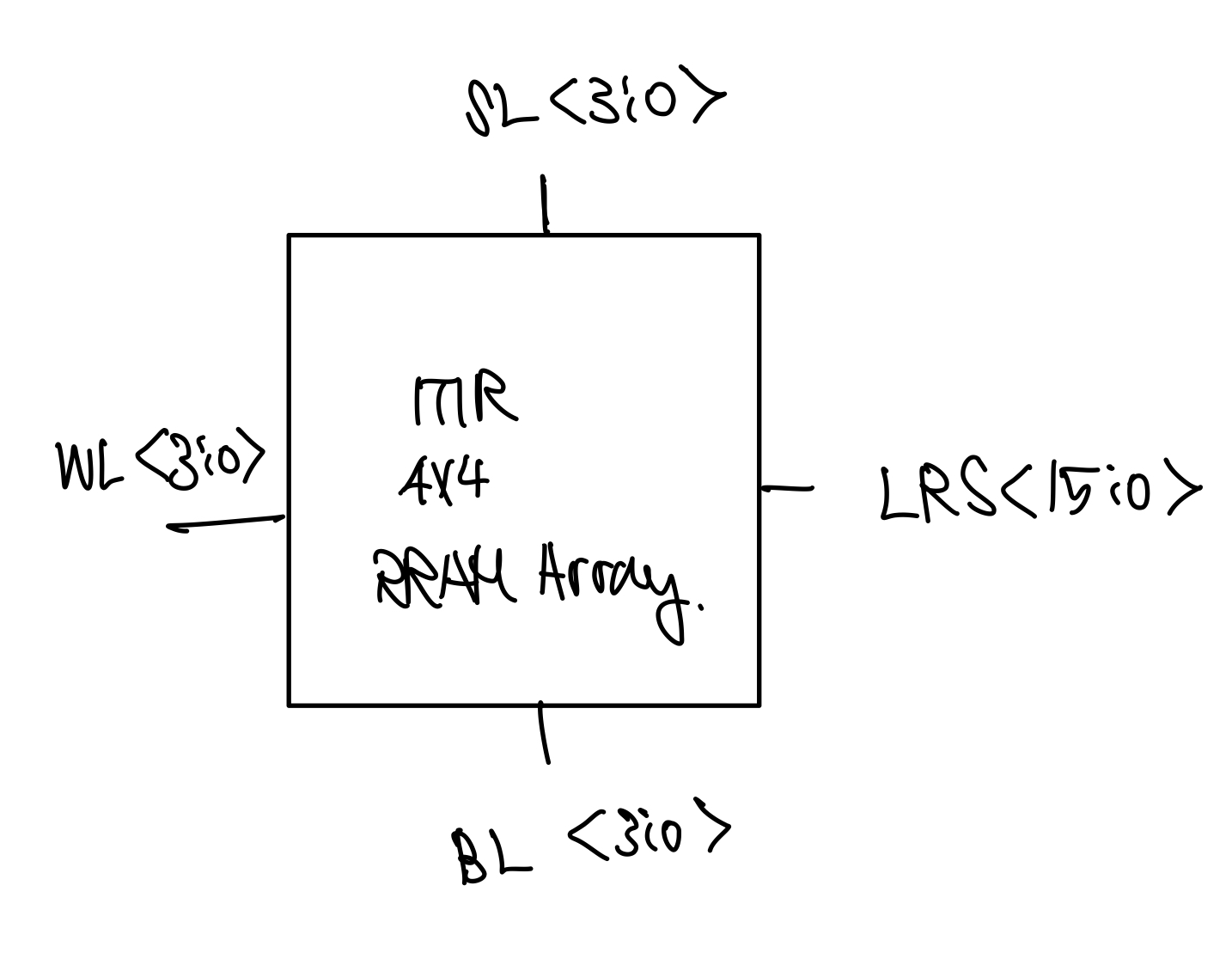

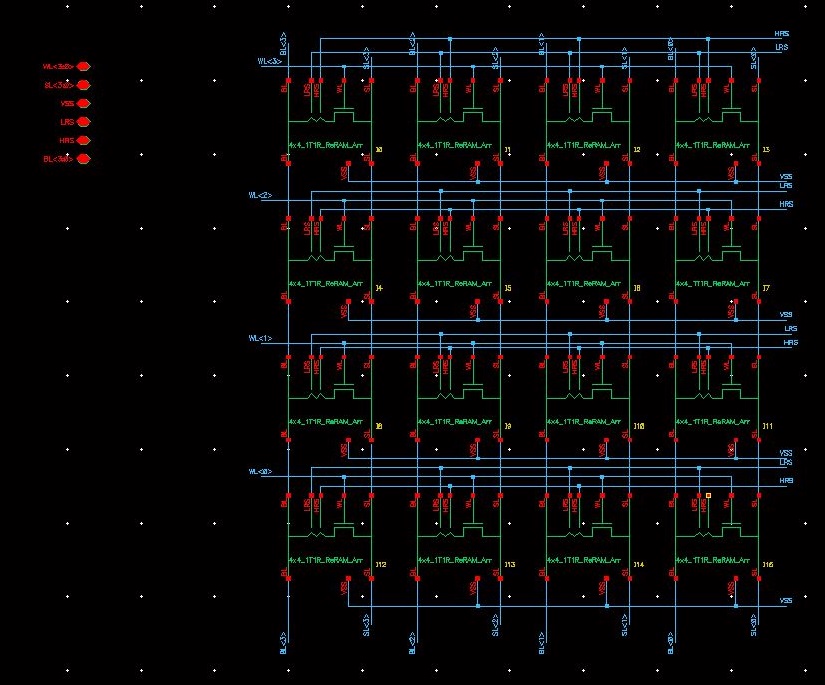

그렇게 만든 RRAM을 4x4 로 만들어서 vector machine에 이용할 것 인데,

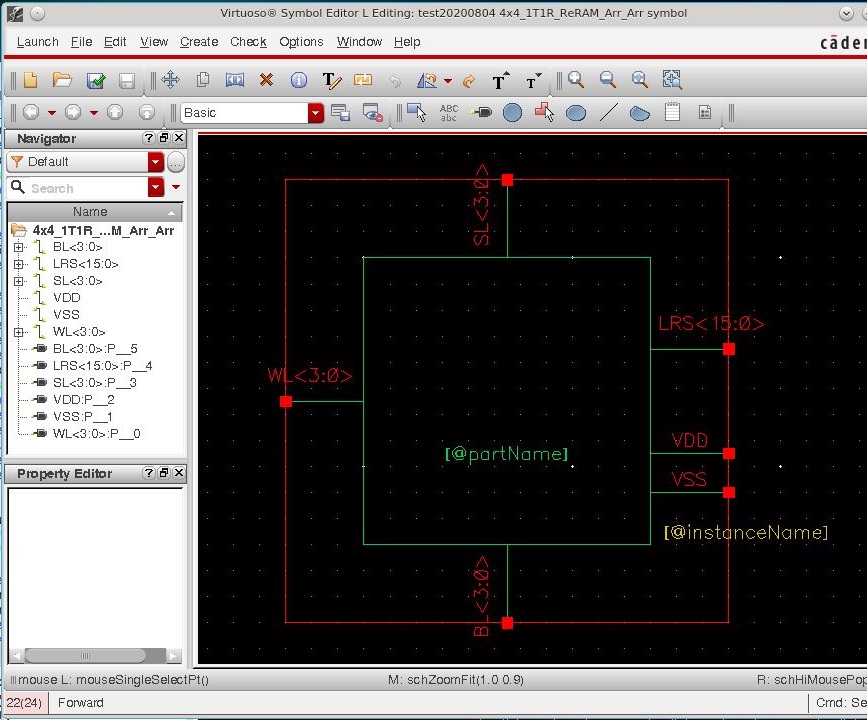

제가 제작할 부분이 아래 그림과 같습니다.

안에 들어갈 어레이는 구글링을 통해서 좀 찾았는데,

여기서 LRS input이 16개나 들어가는 이유는 실제 RRAM 동작에서는 R을 하나로 조작하는데, 우리는 임의로 만들었기 때문에 LRS와 HRS를 선택해주는 스위치가 필요하고 이에따라 input이 들어가게 됩니다.

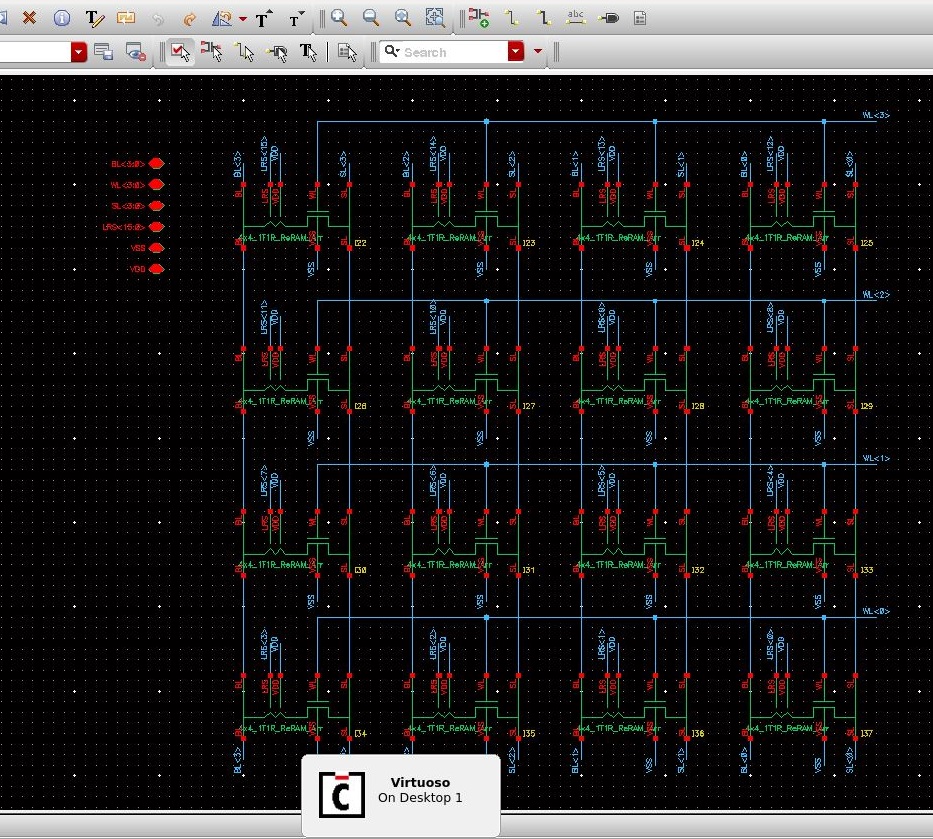

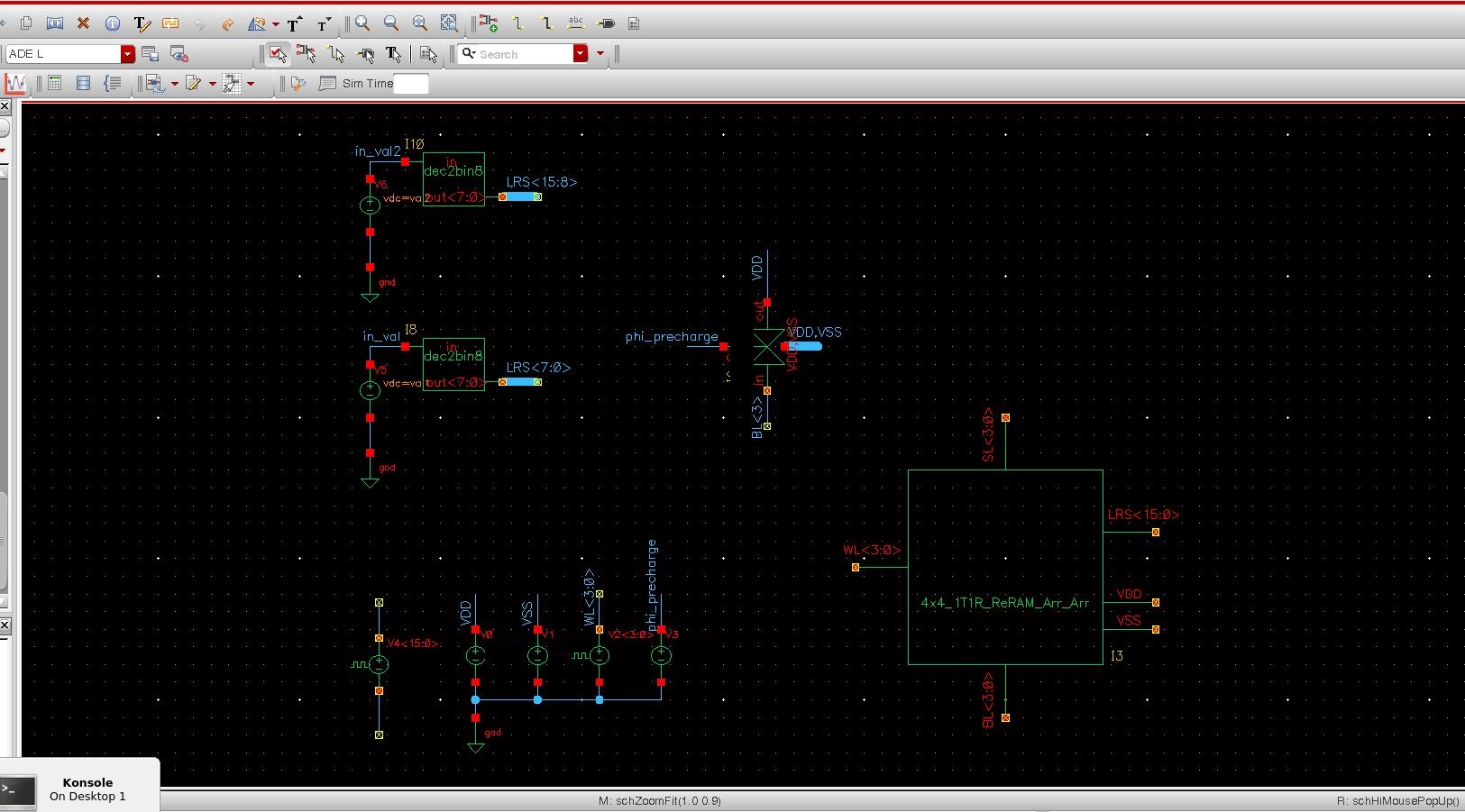

그렇게 스키메틱을 작성해보면,

이런식으로 바디가 있는 nfet을 이용해서 제작해주고,

이를 cellview로 만들어서 하나로 합칩니다.

이런식으로 cell을 만들어줍니다. (BL, SL은 아래 하나씩 더 복사해서 붙임)

이렇게 만든 cell들을 이용해서 4x4 array를 만들어줬는데, 생각해보니까 LRS와 HRS를 16개 개별적으로 조정해서 써야하기 때문에 처음부터 수정!

각각의 array를 뽑아서 InputOutput Pin으로 만들어서 다시 크게 Cellview를 제작합니다.

아까 위에서 그린 그림과 비슷하게 그려서 저장!

옆에는 테스트 벤치를 만들어줬는데, LRS는 decimal을 binary로 만들어서 값을 쉽게 넣을 수 있도록 만들었고, 간단한 버전으로 확인하기 위해서 SL은 VSS로 고정시켜놓고 테스트해 볼 것입니다.

BL을 충전시켜넣고 방전 여부에 따라서 Sense Amp가 감지하는 것이기 때문에 precharge를 이용해서(일종의 스위치) BL을 Vdd로 충전시켜둡니다.

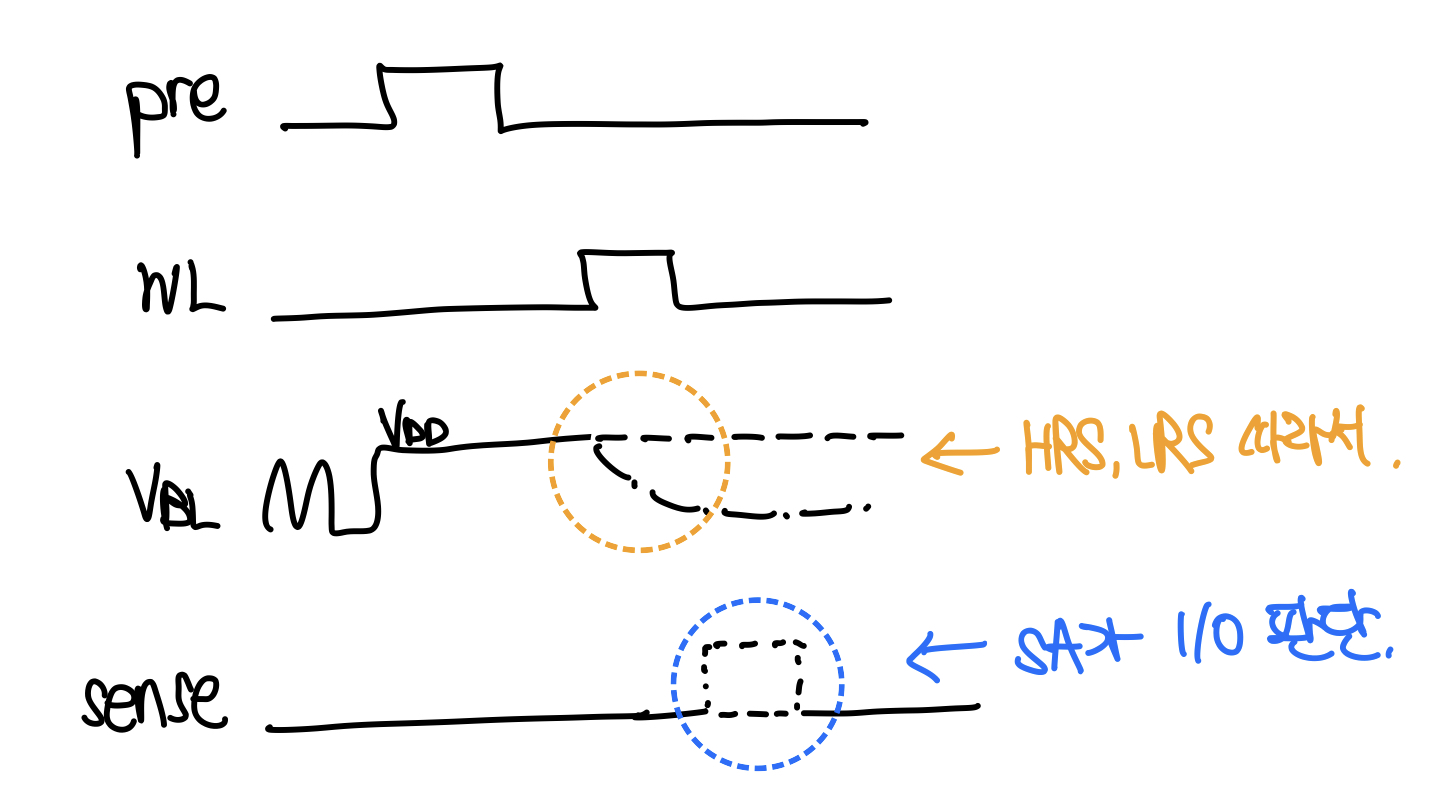

이제 timing diagram을 그려보면서 값을 어떻게 줄지 계획할 것인데, (아래그림)

precharger를 이용해서 BL을 VDD로 충전시켜놓고, WL이 들어오면 ON이 돼서 전류가 흐르게 되는데 HRS인 경우 저항이 커서 거의 방전이 되지 않아 logic 0을 의미하게 되고, LRS인 경우 저항이 작아 방전이 많이 되서 logic 1을 의미하게 됩니다. 이 logic val 결정하는 것은 SA가 담당하게 됩니다.

이런 흐름으로 값을 측정할 것이고 추후 정리가 되면 결과도 올리도록 하겠습니다.

reference :

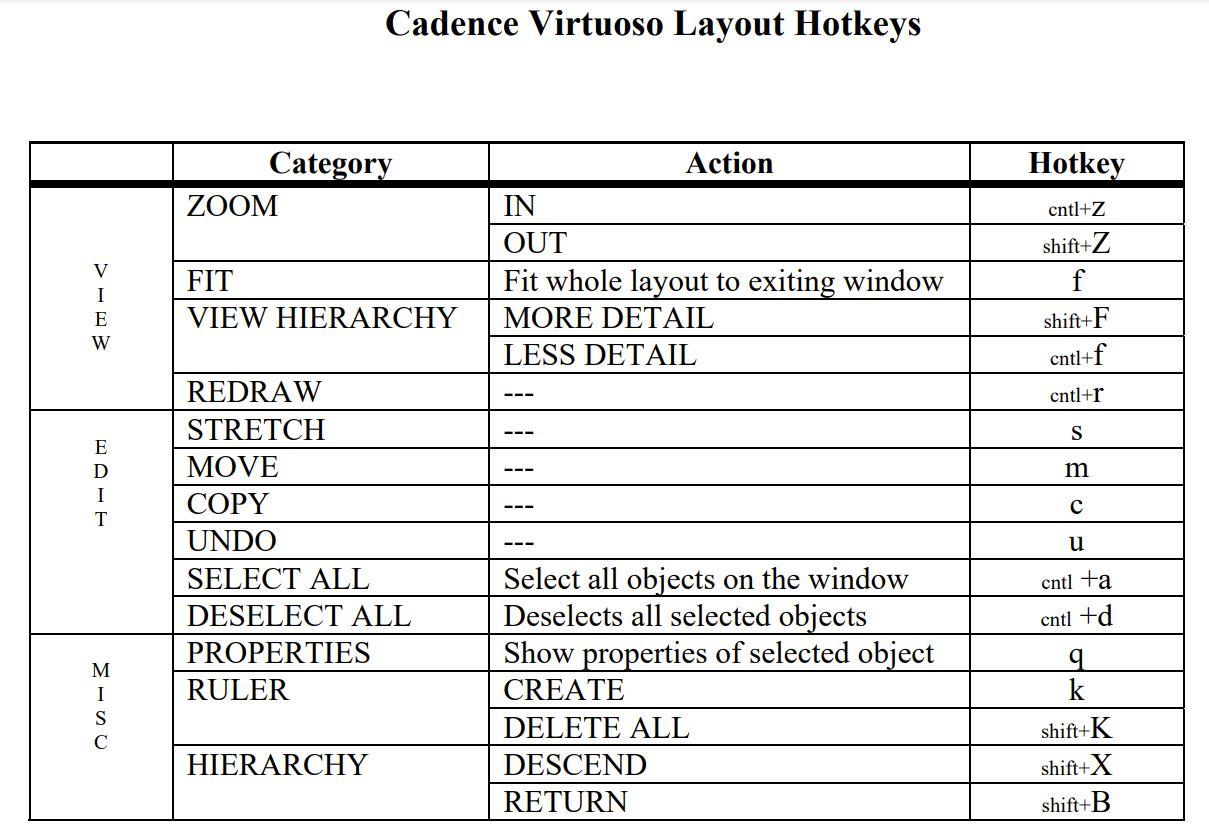

webpages.uidaho.edu/ece/ee/analog/suatay/cadence/Cadence%20Layout%20Hotkeys.pdf

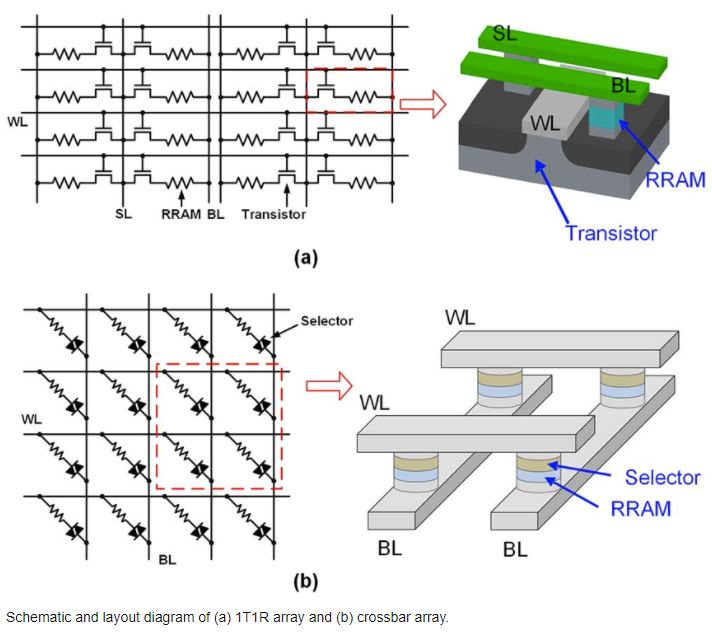

Fig. 1. Schematic and layout diagram of (a) 1T1R array and (b) crossbar...

Download scientific diagram | Schematic and layout diagram of (a) 1T1R array and (b) crossbar array. from publication: Investigation of Single-Bit and Multiple-Bit Upsets in Oxide RRAM-Based 1T1R and Crossbar Memory Arrays | In this paper, the susceptib

www.researchgate.net

최근댓글